Projects

From Wikipedia, the free encyclopedia

A compact, synthesizable RV32I-style RISC‑V core implemented in Verilog. The design contains a simple program counter, register file, ALU, control unit, and synchronous instruction/data memories designed to infer Intel M9K BRAMs. The repository includes reusable RTL components (muxes, adders), a small testbench suite compatible with ModelSim and Verilator, and documentation for Quartus-based FPGA builds.

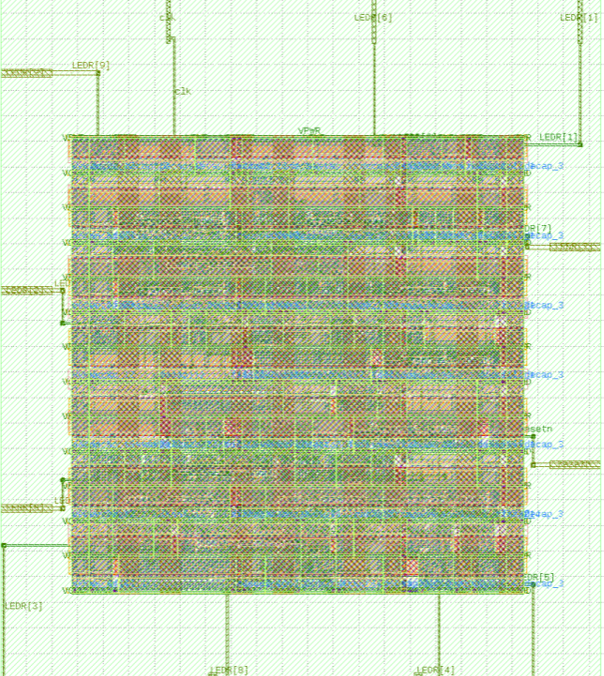

Verification used directed testbenches and waveform inspection to validate instruction execution. An OpenLane flow was used to generate a GDS II layout, demonstrating an end-to-end path from RTL to a fabrication-ready layout.

Verification used directed testbenches and waveform inspection to validate instruction execution. An OpenLane flow was used to generate a GDS II layout, demonstrating an end-to-end path from RTL to a fabrication-ready layout.

RV32I-style core: RTL → FPGA → OpenLane GDS

Built during AgentHacks with teammates, dExtra Tools extends the Dex browser agent by adding a Working Memory system, a Planning Agent, and a Frontend-WebSocket bridge (get_selected_text). The system integrates with an MCP backend and enables deeper, real-time browser interaction for agent workflows. Won Dex Best Browser Agent at AgentHacks.